Overview

This project demonstrates complete hardware–software integration.

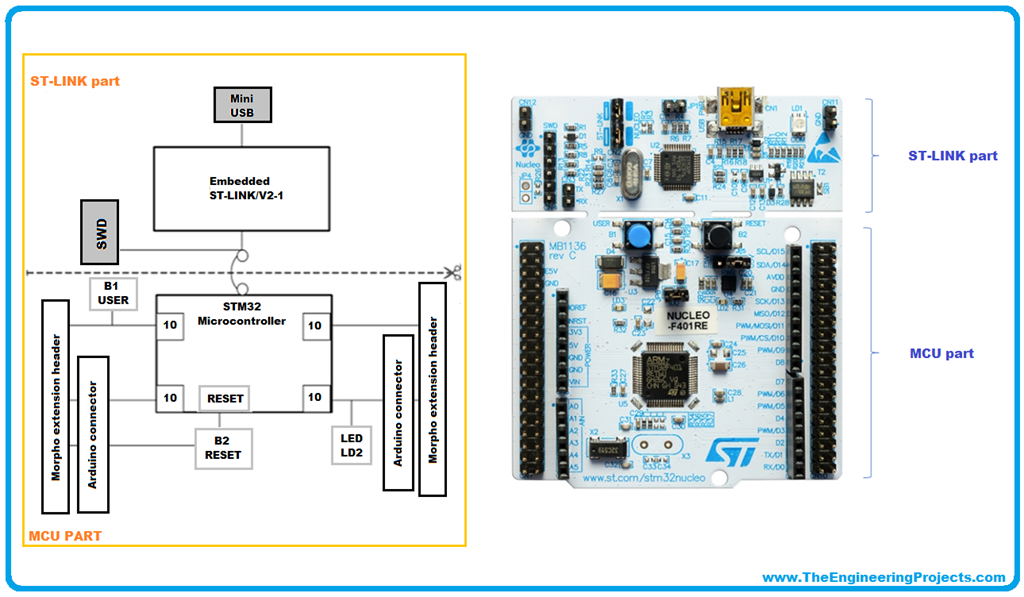

The STM32 embedded system reads sensor data (temperature, distance), displays it on an LCD screen, and communicates via UART/I²C interfaces.

In parallel, a pipelined RISC-V processor was implemented in VHDL using a 5-stage architecture (IF, ID, EX, MEM, WB) with hazard detection and forwarding logic.

The two systems were connected to simulate communication between a control microcontroller and a dedicated processing unit implemented on an FPGA.

Quartus II simulations verified pipeline timing and data coherence, while STM32 testing ensured real-time operation and memory efficiency.

🛠️ Technologies / Tools

- STM32 (Nucleo) — Sensors, LCD, UART/I²C communication

- VHDL (Quartus II) — RISC-V pipeline implementation

- FPGA (Altera DE2) — Hardware testing and timing validation

- Languages: Embedded C, VHDL

- Tools: Oscilloscope, Serial Monitor, Quartus Timing Simulation

🎯 Key Learnings

- Integration between embedded systems and hardware-simulated processors

- Mastery of UART communication and real-time scheduling

- Modular pipeline design and hazard management with timing verification