Overview

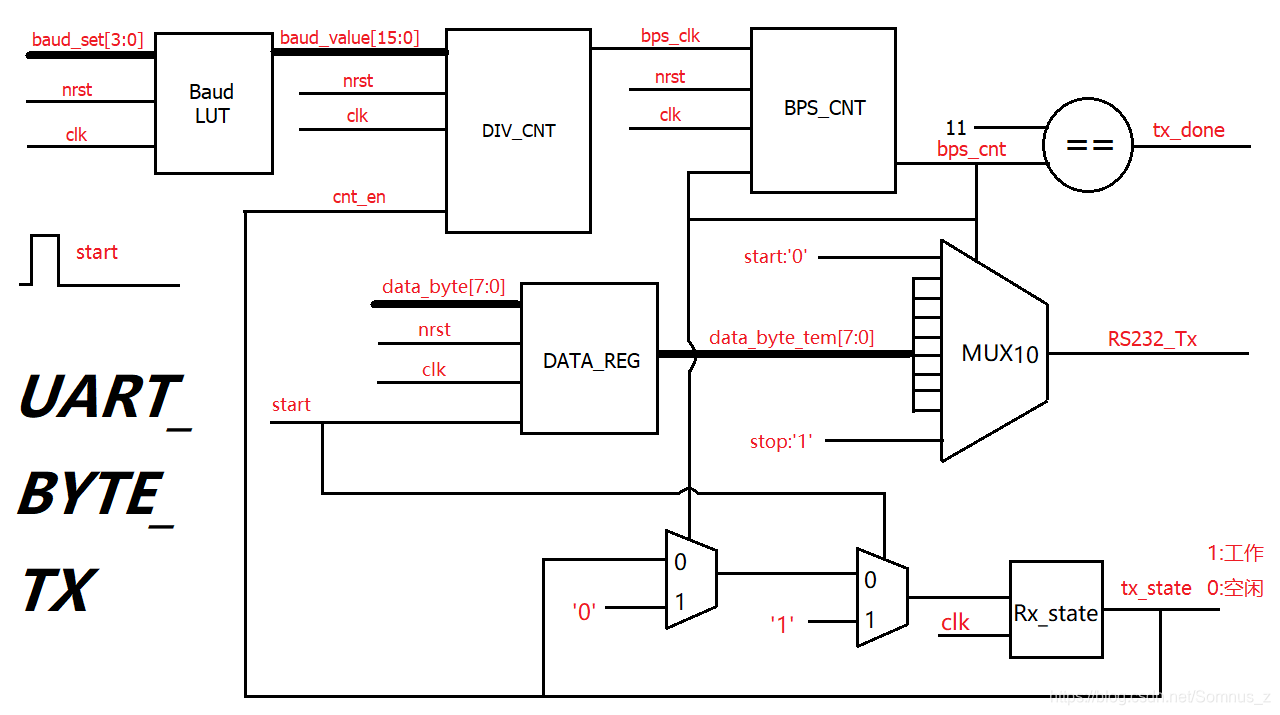

Design of a complete UART communication system using VHDL, including parallel-to-serial and serial-to-parallel conversion, a baud rate generator, and robust finite state machines (FSM) for TX and RX modules.

The system was built without a shared clock, relying on asynchronous timing and real-time synchronization.

A MAX232 chip provided CMOS to RS-232 level shifting for integration with a PC terminal (Putty).

The design was also integrated with a traffic light controller, showcasing real-world embedded communication between hardware modules.

🛠️ Technologies / Tools

- Languages: VHDL

- Hardware: MAX232, Altera DE2 (FPGA)

- Software: Quartus II, Putty

- Testing: Loopback, Testbench simulations

🎯 Key Learnings

- Disciplined RTL design and FSM implementation

- Real-time UART communication with hardware-level timing control

- Asynchronous systems without a shared clock

- Full UART loopback debugging and integration with larger embedded systems